用于逻辑综合的VHDL

全新正版 极速发货

¥ 60.25 6.8折 ¥ 89 全新

仅1件

送至北京市朝阳区

运费快递 ¥3.50

作者Andrew Rushton 著 刘雷波 等 译

出版社北京航空航天大学出版社

ISBN9787512413665

出版时间2014-01

装帧平装

开本16开

定价89元

货号1200895853

上书时间2024-11-22

评价26825好评率 99.91%

- 最新上架

商品详情

- 品相描述:全新

- 商品描述

-

目录

第1章引言

1.1VHDL设计周期

1.2VHDL的起源

1.3标准化过程

1.4VHDL标准的统一

1.5可移植性

第2章寄存器传输级设计

2.1RTL设计阶段

2.2电路举例

2.3确定数据运算

2.4确定数据精度

2.5确定所用资源

2.6运算资源的配置

2.7设计控制器

2.8设计复位机制

2.9RTL设计的VHDL描述

2.10综合结果

第3章组合逻辑

3.1设计单元

3.2实体和结构体

3.3仿真模型

3.4综合模板

3.5信号和端口

3.6初始值

3.7简单信号的赋值

3.8条件信号赋值

3.9受选信号赋值

3.10样例

第4章基本类型

4.1可综合的类型

4.2标准类型

4.3标准操作符

4.4比特(bit)类型

4.5布尔(boolean)类型

4.6整数(Integer)类型

4.6.1TypeInteger

4.6.2自定义整数

4.6.3整数子类型

4.6.4综合解释

4.7枚举类型

4.8多值逻辑类型

4.9记录

4.10数组

4.11集合体、字符串和位串

4.12属性

4.12.1整数类型和枚举类型

4.12.2数组属性

4.13关于被选中信号赋值的几个问题

第5章操作符

5.1标准操作符

5.2操作符的优先级

5.3布尔操作符

5.4比较操作符

5.4.1综合解释

5.4.2整数类型和枚举类型

5.4.3数组类型

5.5移位操作符

5.5.1固定移位位数

5.5.2可变移位位数

5.6算术操作符

5.6.1综合解释

5.6.2正号

5.6.3负号

5.6.4求绝对值操作符abs

5.6.5加法操作符

5.6.6减法操作符

5.6.7乘法操作符

5.6.8除法操作符

5.6.9求模操作符

5.6.10求余操作符

5.6.11幂指数操作符

5.7拼接操作符

第6章综合类型

6.1综合类型系统

6.2使程序包可见

6.2.1情景1:由供应商提供的VHDL—2008程序包

6.2.2情景2:使用VHDL—1993兼容程序包

6.2.3VHDL—2008Context(上下文)声明

6.3逻辑类型—StdLogic_1164

6.3.1std_logic—一位逻辑类型

6.3.2std_logic_vector—多位逻辑类型

6.3.3操作符

6.3.4比较操作符

6.3.5布尔操作符

6.3.6移位操作符

6.4数值类型—Numeric_Std

6.4.1所提供的类型

6.4.2Resize函数

6.4.3操作符

6.4.4比较操作符

6.4.5布尔操作符

6.4.6移位操作符

6.4.7算术操作符

6.5定点类型—FixedPkg

6.5.1提供的类型

6.5.2溢出模式和下溢模式

6.5.3Resize函数

6.5.4操作符

6.5.5比较操作符

6.5.6布尔操作符

6.5.7移位操作符

6.5.8算术操作符

6.5.9实用函数

6.6浮点类型—Float_Pkg

6.6.1Float类型

6.6.2解释浮点数

6.6.3溢出,下溢和错误模式

6.6.4舍入模式

6.6.5模式选择

6.6.6函数和操作符

6.6.7分类函数

6.6.8操作符

6.6.9比较操作符

6.6.10布尔操作符

6.6.11算术操作符

6.6.12Resize函数

6.6.13实用函数

6.7类型转换

6.7.1位保留转换

6.7.2值保留转换

6.8常数

6.9表达式中的混合类型

6.10顶层接口

第7章Std_Logic_Arith(标准算术逻辑)

7.1Std_Logic_Arith程序包

7.2Std_Logic_Arith的内容

7.2.1位宽调整函数

7.2.2运算符

7.2.3比较运算符

7.2.4布尔运算符

7.2.5算术运算符

7.2.6移位函数

7.3类型转换

7.4常数

7.5表达式中混合类型

第8章时序VHDL

8.1进程

8.1.1进程分析

8.1.2组合进程

8.1.3Wait语句

8.1.4wait语句的位置

8.2信号赋值

8.3变量

8.3.1声明

8.3.2初始值

8.3.3使用变量

8.4if语句

8.5Case语句

8.6锁存器推断

8.7循环

8.7.1ForLoops

8.7.2Exit语句

8.7.3Next语句

8.8样例

第9章寄存器

9.1基本的D类型寄存器

9.2仿真模型

9.3综合模型

9.4寄存器模板

9.4.1基本模板

9.4.2If语句模板

9.4.3敏感列表模板

9.4.4确定Wait语句的位置

9.4.5指定有效边沿

9.5寄存器类型

9.6时钟类型

9.7时钟门控

9.8数据门控

9.9异步复位

9.9.1异步复位的仿真模型

9.9.2异步复位模板

9.10同步复位

9.11寄存器化变量

9.12初始值

第10章层次结构

10.1元件作用

10.2间接绑定

10.2.1元件实例

10.2.2元件声明

10.2.3配置说明

10.2.4默认绑定

10.2.5间接绑定过程总结

10.3直接绑定

10.4元件程序包

10.5参数化元件

10.5.1类属实体

10.5.2使用类属元件

10.5.3参数化的结构体

10.5.4类属参数类型

10.6生成语句

10.6.1ForGenerate语句

10.6.2IfGenerate语句

10.6.3生成语句中的元件实例

10.7样例

10.7.1伪随机二进制序列(PRBS)发生器

10.7.2脉动(Systolic)处理器

第11章子程序

11.1子程序的作用

11.2函数

11.2.1函数的使用

11.2.2函数的声明

11.2.3初始值

11.2.4具有未限定参数的函数

11.2.5非限定性返回值

11.2.6多个返回

11.2.7函数重载

11.3操作符

11.3.1内置操作符

11.3.2操作符重载

11.4类型转换

11.4.1内置类型转换

11.4.2自定义类型转换

11.5过程

11.5.1过程参数

11.5.2具有非限定性参数的过程

11.5.3使用Inout参数

11.5.4信号参数

11.6声明子程序

11.6.1局部子程序声明

11.6.2程序包中的子程序

11.6.3使用程序包

11.7样例

第12章特殊结构

12.1三态

12.2有限状态机

12.2.1两个进程,一个译码器

12.2.2两个进程,两个译码器

12.2.3一个进程,一个译码器

12.2.4状态编码

12.2.5非法状态和复位

12.3RAMs和寄存器堆

12.3.1异步读,同步写

12.3.2同步先读后写

12.3.3同步先写后读

12.3.4RAM读优化

12.3.5获得寄存器堆

12.3.6复位

12.4译码器和ROMs

12.4.1Case语句译码器

12.4.2查找表译码器

第13章测试平台

13.1测试平台

13.2组合测试平台

13.3验证响应

13.4时钟和复位

13.5其他标准类型

13.6无关输出

13.7打印响应值

13.8使用TextIO读数据文件

13.9读标准类型

13.10TextIO错误处理

13.11综合类型的TextIO

13.12自定义类型的TextIO

13.13样例

……

第14章库

第15章案例分析

附录A程序包列表

附录B法参考

参考文献

内容摘要

《国外数字系统设计经典教材系列:用于逻辑综合的VHDL(第3版)》侧重于介绍面向逻辑综合的VHDL程序的编写方法,全面介绍了可综合的VHDL语法条款。但是,考虑到测试工作的重要性,《国外数字系统设计经典教材系列:用于逻辑综合的VHDL(第3版)》也介绍了一部分最为实用的与编写测试平台有关的VHDL语法。《国外数字系统设计经典教材系列:用于逻辑综合的VHDL(第3版)》的读者对象是数字系统设计工程师和正在学习逻辑综合技术的硕士研究生。

为你推荐

中药贴敷疗法(1988年一版一印) 中国医药科技出版社出版

八品无锡

¥239.00

伤寒论与临证——广东科技出版社

六品梅州

¥89.00

马克思恩格斯全集(46 上 )【大32开 精装本 全黑脊黑面(皮)库存未翻阅

九五品北京

¥10.00

封神演义:精装全一册,1958年初版 作家出版社

七五品天津

¥198.00

重庆出版社连环画稿纸

八五品重庆

¥2000.00

倚天屠龙记(4册全) 海峡文艺出版社

八品重庆

¥25.00

五四运动史

八五品无锡

¥700.00

毛泽东选集( 一卷本32开)

七品桂林

¥36.00

1981年《颜真卿 第二册》精装函盒8开本全1册,"中国书法",文物出版社一版一印,私藏无写划印章水迹,品好如图,现货实物拍照。

九品太原

¥1000.00

笑傲江湖(签名本)

九品泰州

¥20000.00

毛主席论人民战争

八品驻马店

¥168.00

彩色连环画!《乌龙院》大长篇漫画系列!(卷1-7、10-14、19,20,21,28,29,30,31,32)20册合售

八品北京

¥150.00

91_黑皮和田籽料

九五品滨州

¥455.00

石头记

八五品重庆

¥294.00

毛泽东选集 1 4卷

八五品青岛

¥669.00

《林海雪原》~作家出版社 57年版!

七五品齐齐哈尔

¥30.00

青春之歌

八品周口

¥5.00

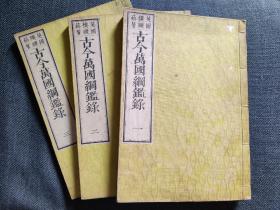

1874年《古今万国纲鉴录》3册全

八五品亚洲

¥6980.00

针灸大成 〔明〕杨继洲著 人民卫生出版社 1958年印

八五品北京

¥1000.00

书剑恩仇录(上下) 百花文艺出版社

八品上海

¥5.00

— 没有更多了 —

微信扫码逛孔网

无需下载

就是封面有点瑕疵,不妨碍阅读也就罢了

书香味很纯正!😁👍🏻👍🏻👍🏻