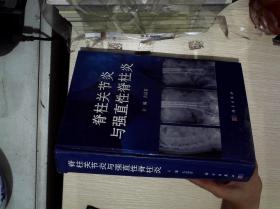

数字逻辑与EDA设计

¥ 14.84 2.7折 ¥ 56 八五品

仅1件

广东东莞

认证卖家担保交易快速发货售后保障

作者丁磊

出版社人民邮电出版社

出版时间2018-09

版次1

装帧平装

上书时间2024-09-10

- 店主推荐

- 最新上架

商品详情

- 品相描述:八五品

图书标准信息

- 作者 丁磊

- 出版社 人民邮电出版社

- 出版时间 2018-09

- 版次 1

- ISBN 9787115459343

- 定价 56.00元

- 装帧 平装

- 开本 16开

- 纸张 胶版纸

- 页数 308页

- 字数 1千字

- 【内容简介】

- 全书共分三个部分:经典篇、现代篇及实验篇,经典篇(第1-3章)主要介绍数字电路的基本概念、基础知识以及组合与时序逻辑电路的分析和设计方法。现代篇(第4-7章)介绍Verilog HDL的基本语法以及基于Verilog HDL和EDA工具的数字电路设计方法,其中第4、5章介绍基本概念和Verilog HDL语法,并给出了几个详细例子的设计流程,是设计的基础。第6、7章介绍基本组合逻辑电路和时序电路的设计、综合及验证方法,其中第7章的综合例子由浅入深,尝试引导读者进行实际应用的设计。实验篇(第8章)是配合第1-7章的实验部分,主要介绍自主研发的能完全满足本课程实验需求的实验箱、基于此实验箱的数字逻辑实验,以及用EDA工具进行数字逻辑设计、仿真及在实验箱上进行验证。

- 【作者简介】

- 1986、9-1990、7 广州华南理工大学自动化系本科 1990、7-1993、4 广州华南理工大学自动化系硕士 1993、5至今 广州广东工业大学计算机学院任教 纵向、横向科研项目累计人民币伍佰万元,2002、2003连续获得佛山市科技进步三等奖。主持编写 《数字逻辑与EDA设计》《数字逻辑与EDA设计实验指导书》

- 【目录】

-

第 1章 数字逻辑基础

1.1 概述

1.1.1 数字信号及模拟信号

1.1.2 数字抽象

1.1.3 数字信号传输时对“0”、“1”的处理

1.2 数制与码制

1.2.1 数制

1.2.2 码制

1.2.3 常用编码

1.3 数字逻辑设计基础

1.3.1 逻辑代数

1.3.2 逻辑函数的表示方法

1.3.3 逻辑函数的化简

1.3.4 逻辑门电路

习题

第 2章 组合逻辑电路

2.1 概述

2.2 组合逻辑电路的分析

2.2.1 组合逻辑电路的分析方法

2.2.2 组合逻辑电路的分析举例

2.3 常用的组合逻辑电路

2.3.1 编码器

2.3.2 译码器

2.3.3 数据选择器

2.3.4 数值比较器

2.3.5 加法器

2.3.6 乘法器

2.4 组合逻辑电路的设计

2.4.1 组合逻辑电路的设计方法

2.4.2 组合逻辑电路的设计举例

2.4.3 利用已有组合集成电路实现其他组合逻辑函数

2.5 组合逻辑电路的时序分析

习题

第3章 时序逻辑电路

3.1 概述

3.1.1 时序电路的基本概念及特点

3.1.2 时序电路逻辑功能的表示方法

3.1.3 时序电路的分类

3.2 锁存器及触发器

3.2.1 锁存器

3.2.2 触发器

3.3 时序电路的分析

3.3.1 时序电路的分析方法

3.3.2 时序电路的分析举例

3.4 常用的时序逻辑电路

3.4.1 寄存器

3.4.2 计数器

3.5 时序电路的设计方法

3.5.1 时序电路的设计方法

3.6 时序逻辑电路时序分析的基本概念

习题

第4章 硬件描述语言Verilog HDL

4.1 HDL简介

4.1.1 关于硬件描述语言

4.1.2 Verilog HDL的特点

4.1.3 硬件描述语言的发展趋势

4.2 初步认知

4.2.1 门级风格的描述

4.2.2 数据流风格的描述

4.2.3 行为风格的描述

4.2.4 测试平台的编写

4.2.5 使用Modelsim进行仿真

4.2.6 Verilog HDL在电路综合中的应用

4.3 Verilog HDL基本知识

4.3.1 标识符和关键字

4.3.2 编写格式

4.3.3 模块和端口

4.3.4 系统任务和系统函数

4.3.5 常用编译器指令

4.4 数据类型、操作符和表达式

4.4.1 值的种类

4.4.2 数据类型

4.4.3 操作数

4.4.4 操作符

4.4.5 表达式

4.5 数据流建模

4.5.1 关于数据流建模

4.5.2 连续赋值语句

4.5.3 延迟

4.6 行为级建模

4.6.1 过程结构

4.6.2 时序控制

4.6.3 语句块

4.6.4 过程性赋值

4.6.5 过程性连续赋值

4.6.6 连续赋值、过程性赋值和过程性连续赋值

4.6.7 分支语句

4.6.8 循环控制语句

4.6.9 任务和函数

4.7 结构建模

4.7.1 Verilog HDL的4个抽象层次

4.7.2 内置基本门级元件

4.7.3 结构建模

4.7.4 用户自定义基本元件(UDP)

4.8 测试平台及测试激励的建立

4.8.1 关于测试平台

4.8.2 测试激励的建立

4.9 良好的编程风格

习题

第5章 基于EDA的数字逻辑电路设计基础

5.1 EDA技术简介

5.1.1 EDA技术及其发展

5.1.2 EDA技术实现的目标

5.1.3 EDA和传统设计方法的比较

5.1.4 EDA技术的发展趋势

5.2 EDA设计流程及工具

5.2.1 数字系统设计的一般步骤

5.2.2 EDA工具及其作用

5.3 FPGA简介

5.3.1 关于FPGA

5.3.2 FPGA的基本分类

5.3.3 FPGA的体系结构

5.3.4 FPGA主流厂商简介

5.3.5 集成开发环境Libero IDE

5.4 IP核基础

5.4.1 IP技术概述

5.4.2 Actel IP核简介

5.5 EDA开发综合实例1:Modelsim的使用

5.5.1 门级(结构)风格的描述

5.5.2 数据流风格的描述

5.5.3 行为风格的描述

5.5.4 混合风格的描述

5.5.5 编写测试平台

5.5.6 在Modelsim中进行仿真

5.6 EDA开发综合实例2:Libero IDE完整设计流程

5.6.1 真值表

5.6.2 逻辑表达式

5.6.3 用Verilog描述2-4译码器

5.6.4 编写测试平台

5.6.5 FPGA开发完整流程

5.7 EDA开发综合实例3:SmartDesign的使用

5.7.1 使用半加器构造全加器

5.7.2 与现有的全加器对比

5.7.3 改造为2位串行进位加法器

5.7.4 调用IP核创建2位串行进位加法器

5.8 本章小结

第6章 基于EDA的组合电路设计、综合及验证

6.1 基本逻辑门电路

6.1.1 基本逻辑门电路的Verilog设计

6.1.2 基本逻辑门电路的综合

6.1.3 测试平台设计

6.1.4 基本逻辑门电路的验证

6.2 编码器

6.2.1 8-3编码器(一)

6.2.2 8-3编码器(二)

6.2.3 8-3编码器(三)

6.2.4 74HC148设计

6.3 译码器

6.3.1 3-8译码器(一)

6.3.2 3-8译码器(二)

6.3.3 扩展型4511设计

6.4 数据选择器

6.4.1 4选1数据选择器(一)

6.4.2 4选1数据选择器(二)

6.4.3 4选1数据选择器(三)

6.4.4 4选1数据选择器(四)

6.5 数值比较器

6.5.1 4位数值比较器(一)

6.5.2 4位数值比较器(二)

6.5.3 74HC85设计

6.6 加法器

6.6.1 1位半加器(一)

6.6.2 1位半加器(二)

6.6.3 1位半加器(三)

6.6.4 1位全加器(一)

6.6.5 1位全加器(二)

6.6.6 1位全加器(三)

6.6.7 4位串行(行波)进位加法器(一)

6.6.8 4位串行进位加法器(二)

6.6.9 4位超前进位加法器

6.7 乘法器

6.7.1 无符号4位乘法器

6.7.2 有符号4位乘法器

6.8 组合逻辑电路的竞争冒险问题

6.8.1 竞争冒险分析

6.8.2 竞争冒险的解决

6.8.3 更进一步的分析

6.9 组合逻辑电路的综合性实例

6.9.1 实例一:补码生成电路

6.9.2 实例二:有符号数的比较电路设计

6.9.3 实例三:有符号数的加法电路设计

6.9.4 实例四:八位二进制数转换为十进制数电路设计

6.9.5 实例五:编码器扩展电路设计

习题

第7章 基于EDA的时序电路设计、综合及验证

7.1 锁存器

7.1.1 RS锁存器(基本)一

7.1.2 RS锁存器(基本)二

7.1.3 门控D锁存器一

7.1.4 门控D锁存器二

7.1.5 带清零D锁存器一

7.1.6 带清零D锁存器二

7.2 触发器

7.2.1 D触发器一

7.2.2 D触发器二(异步清零边沿触发)

7.2.3 D触发器三(同步清零边沿触发型)

7.2.4 JK触发器

7.2.5 RS触发器

7.2.6 T触发器(异步清零)

7.3 寄存器

7.3.1 基本寄存器一

7.3.2 基本寄存器二(异步清零异步置1)

7.3.3 移位寄存器一(并入并出单向左移)

7.3.4 移位寄存器二(并入串出单向左移)

7.3.5 移位寄存器三(串入并出单向左移)

7.3.6 移位寄存器四(串入串出单向移位)

7.4 寄存器传输

7.4.1 基本概念

7.4.2 微操作种类

7.4.3 单寄存器微操作

7.5 计数器

7.5.1 计数器一(四位二进制加法)

7.5.2 计数器二(带置数)

7.5.3 74HC161设计

7.6 有限状态机

7.6.1 有限状态机概述

7.6.2 有限状态机的设计方法

7.6.3 基于状态转换图(STG)的FSM设计实例

7.6.4 基于算法状态图(ASM)的FSM设计实例

7.6.5 状态机设计总结

7.7 时序逻辑电路的综合性实例

7.7.1 实例一:计数器数码管显示电路设计

7.7.2 实例二:4位数码管动态扫描显示电路的设计

7.7.3 实例三:交通灯控制器

7.7.4 实例四:键盘扫描器和编码器

7.7.5 实例五:短跑计时器

习题

第8章 数字逻辑的综合

8.1 关于综合的再介绍

8.1.1 逻辑综合

8.1.2 RTL综合

8.1.3 高级综合

8.2 Verilog HDL基本语句的综合

8.2.1连续性赋值语句

8.2.2过程赋值语句的综合

8.2.3逻辑运算符的综合

8.2.4算术运算符的综合

8.2.5关系运算符的综合

8.2.6移位(shift)运算符的综合

8.2.7 位选择综合

8.2.8条件表达式的综合

8.2.9 always语句的综合

8.2.10 if语句的综合

8.2.11 case语句的综合

8.2.12循环语句的综合

8.2.13 函数的综合

8.2.14任务的综合

8.2.15任意值/高阻的综合

8.2.16 锁存器的综合

8.3 可综合问题

参考文献

点击展开

点击收起

— 没有更多了 —

以下为对购买帮助不大的评价