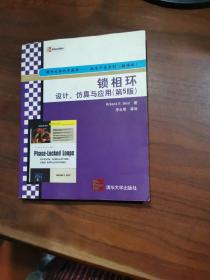

锁相环设计、仿真与应用 正版实物图现货

¥ 108 八五品

仅1件

广东广州

认证卖家担保交易快速发货售后保障

作者贝斯特 著

出版社清华大学出版社

出版时间2007-04

版次1

装帧平装

上书时间2024-12-26

- 店主推荐

- 最新上架

商品详情

- 品相描述:八五品

图书标准信息

- 作者 贝斯特 著

- 出版社 清华大学出版社

- 出版时间 2007-04

- 版次 1

- ISBN 9787302128823

- 定价 39.00元

- 装帧 平装

- 开本 其他

- 纸张 其他

- 页数 353页

- 【内容简介】

-

《锁相环:设计、仿真与应用》(第5版)(翻译版)第1章是简短的引言,介绍锁相环领域的情况。第2章安排涉及混合信号锁相环的理论,设计和混合信号PLL的应用。讨论了不同类型的鉴相器(线性的和数字的),具有电荷泵输出的鉴频鉴相器、环路滤波器(无源和有源)以及压控振荡器。给出了典型混合信号锁相环的应用,例如重定时和时钟恢复,控制马达速度等。

因为频率综合器是DPLL数字锁相环最重要的应用之一,所以单立第3章深入讨论数字锁相环频率综合器。因为相位抖动和寄生边带是频率综合器最烦人的现象,我们给出了不同的解决这些问题的方法,即抗齿隙式电路和高阶环路滤波器。此外,还分析了整数N和分数N两类综合器并说明后者可以非常快地捕获锁定,其特点是在跳频(扩频)应用中具有很大的好处;最新一代的移动电话中,扩频技术将越来越重要。接着说明了简单的频率综合器可以单环实现,而高性能系统中必须使用多环结构。

因为在许多综合器应用中必须采用高阶系统(滤波器),第4章讨论了这样系统的设计,例如高达五阶的锁相环。在高阶环路的设计中,安排极点和零点的位置会是一项困难的工作,利用作者开发的新方法,基于波特图,可以非常容易地进行高阶环路设计。同时,利用作者开发的程序(在随书附有的CDROM中)可以轻松实现系统。该程序可以自动设计和分析高达五阶的锁相环路。该主题在第5章讨论,其中还包括了许多设计例子。在综合一个锁相环电路时,这个程序可以用于模拟系统的动态性能,即锁定和失锁过程。为了研究锁相环在噪声情况下的性能(这在实际中是一般设定情况),用户可以添加任意水平的窄带或宽带噪声。最终,程序显示综合的锁相环波特图和环路滤波器电路图,包括元件值。

第6章阐述全数字锁相环ADPLL的理论、设计和应用,这类PLL引入时间比前面介绍的要晚一些。这几种锁相环中,LPLL与DPLL是连续时间系统,而ADPLL是离散时间器件,所以,会表现出相对较大的波纹(相位抖动)。因此,ADPLL的应用局限在可容忍波纹的情况下,如频移键控(FSK)解码器和类似设备。第7章描述了ADPLL计算机辅助设计和仿真,使用前面讲述过的计算机程序。

因为近年来微控制器和数字信号处理器的速度显著提高,现在许多PLL应用都可以用软件实现。第8章讨论了锁相环领域中软件和硬件折中的考虑,描述了一些可以实现软件PLL(SPLL)的软件算法。

第9章综述通信领域中PLL的应用。包括大多数重要的数字调制方案,例如BSK,QPSK,FSK以及QAM,并且描述了一些专用的PLL电路用于载波和符号同步(如,Costas环,早迟门,积分和复位转移电路),以及采取措施防止符号间干扰(intersymbolinterference,ISI),例如平方根升余弦滤波器。本章的其他主题中也说明了在不增加系统带宽的情况下,如何增加数字通信的符号速率。

第10章列出了当前可以使用的PLL集成电路,它们来自美国、欧洲和日本的制造厂家,包括简短的电路说明。列表中包括单片上完整的PLL系统,锁相环的部分电路模块,如鉴相器和VCO压控振荡器,以及类似锁相环频率综合器的复杂系统或收音机、电视机芯片;还包括单、双模预分频器。

最后,第11章说明使用常规实验室仪器,如示波器、信号发生器等,以及如何测量锁相环的参数。 - 【目录】

-

第1章锁相环简介

第2章混合信号锁相环

第3章锁相频率综合器

第4章高阶环路

第5章混合信号PLL的计算机辅助设计和仿真

第6章全数字PLL(ADPLL)

第7章ADPLL的计算机辅助设计和仿真

第8章软件PLL(SPLL)

第9章通信中的锁相环(PLL)

第10章商用PLL集成电路技术现状

第11章PLL参数的测量

附录A捕捉过程(ThePullProcess)

附录B拉普拉斯变换

附录C数字滤波器基础

参考文献

索引

点击展开

点击收起

相关推荐

— 没有更多了 —

以下为对购买帮助不大的评价