临时通知 :【当天下午5点前基本能发走《特殊情况除外、尽量发、隔天一定能发、提前给单号》】旧书不保证少许几页笔记、在意书友、可以咨询、有问题找我处理【签收快递包裹出现问题、一定要保存外包装、拍照】请注意 我店没发票

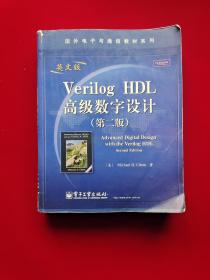

国外电子与通信教材系列:Verilog HDL高级数字设计(第2版)(英文版)

当天发货 实图拍照正版现货、注意描述和图片为准

¥ 85 8.7折 ¥ 98 八品

仅1件

送至北京市朝阳区

运费快递 ¥8.00

作者[美]西勒提 著

出版社电子工业出版社

出版时间2010-04

版次1

装帧平装

货号26-6

上书时间2024-04-09

评价6057好评率 100%

- 在售商品 暂无

- 平均发货时间 4小时

- 好评率 100%

- 最新上架

商品详情

- 品相描述:八品

- 边角有损坏、盖章 有点笔记、不影响阅读

图书标准信息

- 作者 [美]西勒提 著

- 出版社 电子工业出版社

- 出版时间 2010-04

- 版次 1

- ISBN 9787121104770

- 定价 98.00元

- 装帧 平装

- 开本 16开

- 纸张 胶版纸

- 页数 965页

- 字数 1813千字

- 正文语种 英语

- 丛书 国外电子与通信教材系列

- 【内容简介】

-

《VerilogHDL高级数字设计(第2版)(英文版)》依据数字集成电路系统工程开发的要求与特点,利用VerilogHDL对数字系统进行建模、设计与验证,对ASIC/FPGA系统芯片工程设计开发的关键技术与流程进行了深入讲解,内容包括:集成电路芯片系统的建模、电路结构权衡、流水、多核微处理器、功能验证、时序分析、测试平台、故障模拟、可测性设计、逻辑综合、后综合验证等集成电路系统的前后端工程设计与实现中的关键技术及设计案例。书中以大量设计实例叙述了集成电路系统工程开发需遵循的原则、基本方法、实用技术、设计经验与技巧。

《VerilogHDL高级数字设计(第2版)(英文版)》既可作为电子与通信、电子科学与技术、自动控制、计算机等专业领域的高年级本科生和研究生的教材或参考资格,也可用于电子系统设计及数字集成电路设计工程师的专业技术培训。 - 【作者简介】

- 西勒提(MichaelD.Ciletti),科罗拉多大学电气与计算机工程系教授。研究方向包括通过硬件描述语言进行数字系统的建模、综合与验证、系统级设计语言和FPGA嵌入式系统。其著作还有DigitalDesign,FourthEdition(其翻译版和影印版均由电子工业出版社出版)。作者曾在惠普、福特微电子和Prisma等公司进行VLSI电路设计的研发工作,在数字系统和嵌入式系统研究、设计等领域有丰富的研发和教学经历。

- 【目录】

-

1IntroductiontoDigitalDesignMethodology

1.1DesignMethodology-AnIntroduction

1.1.1DesignSpecification

1.1.2DesignPartition

1.1.3DesignEntry

1.1.4SimulationandFunctionalVerification

1.1.5DesignIntegrationandVerification

1.1.6PresynthesisSign-Off

1.1.7Gate-LevelSynthesisandTechnologyMapping

1.1.8PostsynthesisDesignValidation

1.1.9PostsynthesisTimingVerification

1.1.10TestGenerationandFaultSimulation

1.1.11PlacementandRouting

1.1.12PhysicalandElectricalDesignRuleChecks

1.1.13ParasiticExtraction

1.1.14DesignSign-Off

1.2ICTechnologyOptions

1.3Overview

References

2ReviewofCombinationalLogicDesign

2.1CombinationalLogicandBooleanAlgebra

2.1.1ASICLibraryCells

2.1.2BooleanAlgebra

2.1.3DeMorgansLaws

2.2TheoremsforBooleanAlgebraicMinimization

2.3RepresentationofCombinationalLogic

2.3.1Sum-of-ProductsRepresentation

2.3.2Product-of-SumsRepresentation

2.4SimplificationofBooleanExpressions

2.4.1SimplificationwithExclusive-Or

2.4.2KarnaughMaps(SOPForm)

2.4.3KarnaughMaps(POSForm)

2.4.4KarnaughMapsandDont-Cares

2.4.5ExtendedKarnaughMaps

2.5GlitchesandHazards

2.5.1EliminationofStaticHazards(SOPForm)

2.5.2Summary:EliminationofStaticHazardsinTwo-LevelCircuits

2.5.3StaticHazardsinMultilevelCircuits

2.5.4Summary:EliminationofStaticHazardsinMultilevelCircuits

2.5.5DynamicHazards

2.6BuildingBlocksforLogicDesign

2.6.1NAND-NORStructures

2.6.2Multiplexers

2.6.3Demultiplexers

2.6.4Encoders

2.6.5PriorityEncoder

2.6.6Decoder

2.6.7PriorityDecoder

References

Problems

3FundamentalsofSequentialLogicDesign

3.1StorageElements

3.1.1Latches

3.1.2TransparentLatches

3.2Flip-Flops

3.2.1D-TypeFlip-Flop

3.2.2Master-SlaveFlip-Flop

3.2.3J-KFlip-Flops

3.2.4TFlip-Flop

3.3BussesandThree-StateDevices

3.4DesignofSequentialMachines

3.5State-TransitionGraphs

3.6DesignExample:BCDtoExcess-3CodeConverter

3.7Serial-LineCodeConverterforDataTransmission

3.7.1DesignExample:AMealy-TypeFSMforSerialLine-CodeConversion

3.7.2DesignExample:AMoore-TypeFSMforSerialLine-CodeConversion

3.8StateReductionandEquivalentStates

References

Problems

4IntroductiontoLogicDesignwithVerilog

4.1StructuralModelsofCombinationalLogic

4.1.1VerilogPrimitivesandDesignEncapsulation

4.1.2VerilogStructuralModels

4.1.3ModulePorts

4.1.4SomeLanguageRules

4.1.5Top-DownDesignandNestedModules

4.1.6DesignHierarchyandSource-CodeOrganization

4.1.7VectorsinVerilog

4.1.8StructuralConnectivity

4.2LogicSystem,DesignVerification,andTestMethodology

4.2.1Four-ValueLogicandSignalResolutioninVerilog

4.2.2TestMethodology

4.2.3SignalGeneratorsforTestbenches

4.2.4Event-DrivenSimulation

4.2.5TestbenchTemplate

4.2.6SizedNumbers

4.3PropagationDelay

4.3.1InertialDelay

4.3.2TransportDelay

4.4TruthTableModelsofCombinationalandSequentialLogicwithVerilog

References

Problems

5LogicDesignwithBehavioralModelsofCombinationalandSequentialLogic

5.1BehavioralModeling

5.2ABriefLookatDataTypesforBehavioralModeling

5.3BooleanEquation-BasedBehavioralModelsofCombinationalLogic

5.4PropagationDelayandContinuousAssignments

5.5LatchesandLevel-SensitiveCircuitsinVerilog

5.6CyclicBehavioralModelsofFlip-FlopsandLatches

5.7CyclicBehaviorandEdgeDetection

5.8AComparisonofStylesforBehavioralModeling

5.8.1ContinuousAssignmentModels

5.8.2Dataflow/RTLModels

5.8.3Algorithm-BasedModels

5.8.4NamingConventions:AMatterofStyle

5.8.5SimulationwithBehavioralModels

5.9BehavioralModelsofMultiplexers,Encoders,andDecoders

5.10DataflowModelsofaLinear-FeedbackShiftRegister

5.11ModelingDigitalMachineswithRepetitiveAlgorithms

5.11.1IntellectualPropertyReuseandParameterizedModels

5.11.2ClockGenerators

5.12MachineswithMulticycleOperations

5.13DesignDocumentationwithFunctionsandTasks:LegacyorLunacy?

5.13.1Tasks

5.13.2Functions

5.14AlgorithmicStateMachineChartsforBehavioralModeling

5.15ASMDCharts

5.16BehavioralModelsofCounters,ShiftRegisters,andRegisterFiles

5.16.1Counters

5.16.2ShiftRegisters

5.16.3RegisterFilesandArraysofRegisters(Memories)

5.17SwitchDebounce,Metastability,andSynchronizersforAsynchronousSignals

5.18DesignExample:KeypadScannerandEncoder

References

Problems

6SynthesisofCombinationalandSequentialLogic

6.1IntroductiontoSynthesis

6.1.1LogicSynthesis

6.1.2RTLSynthesis

6.1.3High-LevelSynthesis

6.2SynthesisofCombinationalLogic

6.2.1SynthesisofPriorityStructures

6.2.2ExploitingLogicalDont-CareConditions

6.2.3ASICCellsandResourceSharing

6.3SynthesisofSequentialLogicwithLatches

6.3.1AccidentalSynthesisofLatches

6.3.2IntentionalSynthesisofLatches

6.4SynthesisofThree-StateDevicesandBusInterfaces

6.5SynthesisofSequentialLogicwithFlip-Flops

6.6SynthesisofExplicitStateMachines

6.6.1SynthesisofaBCD-to-Excess-3CodeConverter

6.6.2DesignExample:SynthesisofaMealy-TypeNRZ-to-ManchesterLineCodeConverter

6.6.3DesignExample:SynthesisofaMoore-TypeNRZ-to-ManchesterLineCodeConverter

6.6.4DesignExample:SynthesisofaSequenceRecognizer

6.7RegisteredLogic

6.8StateEncoding

……

7DesignandSynthesisofDatapathControllers

8ProgrammableLogicandStorageDevices

9AlgorithmsandArchitecturesforDigitalProcessors

10ArchitecturesforArithmeticProcessors

11PostsynthesisDesignTasks

AVerilogPrimitives

BVerilogKeywords

CVerilogDataTypes

DVerilogOperators

EVerilogLanguageFormalSyntax

FVerilogLanguageFormalSyntax

GAdditionalFeaturesofVerilog

HFlip-FlopandLatchTypes

IVerilog-2001,2005

JProgrammingLanguageInterface

KWebsites

LWeb-BasedResources

Index

为你推荐

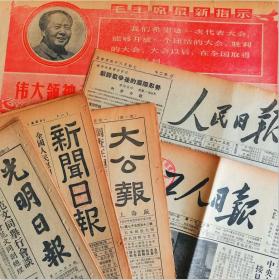

连环画 揭投降派宋江——水浒故事选编

七五品郑州

¥12.00

光明日报新闻内情

九品衡水

¥5.82

民国日记本:光明日记(布面精装)(有地图、插图等)

八五品无锡

¥350.00

毛泽东军事文选【1981年一版一印】

八五品北京

¥350.00

惊封

九品北京

¥13.60

1950年8月11日光明日报

九品合肥

¥196.00

毛泽东选集一卷本,大量商品低价出售请逐页翻看。

八品延边

¥60.00

毛主席万岁(毛主席诗词、毛主席诗词歌曲),如图所示大64开本,有许多彩色像(62幅)

八五品松原

¥850.00

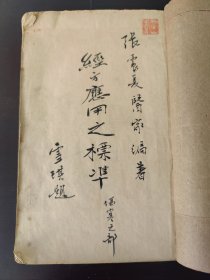

民国《经方应用之标准》(伤寒之部)(中医稿本)张震夏医家编著 雪琪 俞宇 黄应时题 (共写151面全) 张震夏(1922-1976年)江苏无锡人。幼年深痛母病失治,乃有志于岐黄之术。13岁即负笈至江阴拜当地名医吴仁育为师,学习中医内、妇科,兼读经史古文。

八品滨州

¥8800.00

名人与光明日报

九品濮阳市

¥6.00

上海画报出版社·本社 编·《实用人体模特摄影》·64开·06·10

九品丹东

¥18.00

红语录本9本。大小不等。其中毛主席语录皮子里装的是鲁迅语录。 注意有林付主席题词或照片的地方被撕掉了。其他的不缺。标的是一堆的价格。 非全新品,有瑕疵,介意者勿拍。

六品呼和浩特

¥90.00

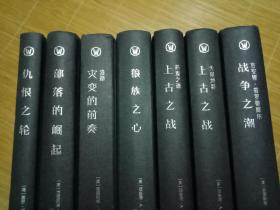

魔兽世界7册和售:《狼族之心》《战争之潮》《上古之战2册》《仇恨之轮》《灾变的前奏》《部落的崛起》32开精装

九品长沙

¥168.00

**报纸——光明日报 1974年2月3日《做批林批孔的先锋——上海第五印染厂》

七五品固原

¥4.00

罕见1967年32开本军队版《毛泽东选集(合订一卷本)》带原始林副主席题词外壳、牛皮书壳和合格证、1966年改横排版、1967年北京一版一印-尊C-5(7788)

八品成都

¥5228.00

来自远方(1、2完结篇)

八品杭州

¥68.00

壁上丹青—山西古代壁画

全新晋中

¥78.90

录像带 汽车专栏(73分钟)为中国喝彩克里姆林宫大型音乐歌舞晚会(缺头75分钟有尾)cvtv1套广告几十个,晚间新闻报道(缺尾)带子总时长2小时58分钟

九品安阳

¥200.00

毛主席诗词 (中华人民共和国二十周年大庆)

八五品苏州

¥120.00

明代四大奇书《张竹坡批评金瓶梅 金圣叹批评水浒传 毛宗岗批评三国演义 李卓吾批评西游记》(另有石头记、红楼梦、三言二拍在售)

九品天水

¥626.00

— 没有更多了 —

微信扫码逛孔网

无需下载

春节期间很慢到货。但是包装很仔细没有损坏。心生感念,尊重店家,祝福生意旺,日子好!愿意再来。

是新书,还有作者签名,非常好